# МИКРОКОНТРОЛЛЕРЫ СЕРИИ 8051:

# ПРАКТИЧЕСКИЙ ПОДХОД

Магда Ю. С.

УДК 621.396.6 ББК 32.872 M12

#### Магда Ю. С.

**M12** Микроконтроллеры серии 8051: практический подход. — М.: ДМК Пресс, 2008. — 228 с.

#### ISBN 5-94074-394-3

В книге рассматривается широкий круг вопросов, связанных с практическим применением популярных микроконтроллеров 8051 и их расширений в системах управления и контроля. Основной упор сделан на практические аспекты разработки цифровых и аналоговых интерфейсов, использования таймеров, визуализации результатов измерений в системах сбора информации. Значительная часть материала посвящена практическому программированию в популярной среде разработки Keil uVision. Приводятся многочисленные примеры разработки несложных аппаратно—программных систем сбора аналоговой и цифровой информации, измерительных систем, систем управления внешними устройствами и т.д. Все приведенные в книге проекты разработаны и проверены на отладочном модуле Rita-51 фирмы Rigel Corp. и могут служить основой при разработке собственных проектов.

ББК 32.872 УДК 621.396.6

Юрий Степанович Магда

# МИКРОКОНТРОЛЛЕРЫ СЕРИИ 8051: практический подход

Главный редактор Мовчан Д. А. dm@dmk-press.ru

Корректор Теренина О. А. Верстка и графика Старцевой Е. М. Дизайн обложки Мовчан А. Г.

Подписано в печать 02.11.2007. Формат 70х100  $\ 1/16$ . Гарнитура «Abbat». Печать офсетная. Усл. печ. л. 21. Тираж 2000 экз.

Издательство «ДМК Пресс» Электронный адрес издательства: www.dmk-press.ru

# Оглавление

| Введение                                                          | 6 |

|-------------------------------------------------------------------|---|

|                                                                   |   |

| Глава 1. Программная архитектура микроконтроллеров 8051 $10^{-1}$ | 0 |

| <b>1.1.</b> Структура внутренней памяти 80511                     | 2 |

| 1.2. Подключение внешней памяти программ и данных 10              | 6 |

| <b>1.3.</b> Система команд микроконтроллера семейства 8051 1      | 7 |

| 1.4. Система прерываний                                           | 3 |

| <b>1.5.</b> Параллельные порты ввода/вывода данных                | 9 |

| Глава 2. Программирование и отладка в среде Keil uVision 3:       | 2 |

| 2.1. Преимущества и недостатки языков высокого уровня 33          | 3 |

| <b>2.2.</b> Создание программ в Keil C51                          | 4 |

| <b>2.3.</b> Синтаксис Keil C51                                    | 5 |

| 2.3.1. Символы, ключевые слова и идентификаторы 4                 | 5 |

| <b>2.3.2.</b> Форматы данных в Keil C51                           | 8 |

| <b>2.3.3.</b> Специальные ключевые слова Keil C51 49              | 9 |

| <b>2.3.4.</b> Операторы и выражения в Keil C51 5-                 | 4 |

| <b>2.3.5.</b> Файлы заголовков Keil C51 5                         | 5 |

| <b>2.4.</b> Управление вводом/выводом в Keil C51 5                | 7 |

| <b>2.5.</b> Операции с памятью 59                                 | 9 |

| 2.6. Программирование ввода/вывода через                          |   |

| последовательный порт60                                           | 0 |

| 2.7. Интерфейс с языком ассемблера6                               | 4 |

| <b>2.7.1.</b> Встроенный ассемблерный код                         | 4 |

| <b>2.7.2.</b> Подпрограммы на ассемблере                          | 1 |

| <b>2.8.</b> Программирование на языке ассемблера в среде Keil 7- | 4 |

|------------------------------------------------------------------|---|

| <b>2.9.</b> Отладка программ в среде Keil uVision                | 3 |

| Глава 3. Использование последовательного порта 9                 | 2 |

| <b>3.1.</b> Запись данных в последовательный порт                | 4 |

| 3.2. Чтение данных из последовательного порта 10                 | 2 |

| 3.3. Прерывание последовательного порта 10.                      | 3 |

| <b>3.4.</b> Работа с последовательным портом в Keil C51 10       | 8 |

| 3.5. Интерфейс систем на базе 8051 с персональным                |   |

| компьютером                                                      | 0 |

| Глава 4. Встроенные таймеры                                      | 7 |

| 4.1. Режим работы таймера в качестве 16-разрядного               |   |

| таймера11                                                        | 9 |

| 4.2. Прерывания таймеров                                         | 4 |

| 4.3. Режим автоперезагрузки                                      | 8 |

| <b>4.4.</b> Счетчики событий                                     | 0 |

| <b>4.5.</b> Таймер 2                                             | 3 |

| 4.5.1. Режим автоперезагрузки таймера 213                        | 4 |

| 4.5.2. Режим захвата таймера 213                                 | 7 |

| 4.6. Аппаратно-программные решения с использованием              |   |

| таймеров                                                         | 5 |

| 4.6.1. Измерение частоты14                                       | 5 |

| 4.6.2. Широтно-импульсная модуляция 15.                          | 3 |

| Глава 5. Обработка дискретных сигналов                           | 8 |

| <b>5.1.</b> Обработка входных данных с использованием SPI 16     | 1 |

| 5.2. Пользовательские интерфейсы ввода дискретных                |   |

| данных                                                           | 4 |

| 5.3. Пользовательские интерфейсы вывода дискретных               |   |

| данных                                                           | 6 |

| Глава 6. Ввод/вывод аналоговых сигналов                          | 2 |

| 6.1. Обработка аналоговых входных сигналов                       | 3 |

| 6.2. Использование цифро-аналоговых                              |   |

| преобразователей                                                 | 5 |

| ОГЛАВЛЕНИЕ                                                           |    |

|----------------------------------------------------------------------|----|

| Глава 7. Отображение информации в системах с микроконтроллерами 8051 | 08 |

| 7.1. Применение семисегментных индикаторов20                         | 09 |

| 7.2. Применение жидкокристаллических индикаторов 2                   | 13 |

| Заключение                                                           | 24 |

# Программная архитектура микроконтроллеров 8051

В этой главе мы рассмотрим основные функциональные узлы популярных микроконтроллеров семейства 8051/8052 и принципы их работы. Здесь же вкратце рассмотрим и систему команд 8051, которая нам пригодится при создании аппаратно-программных проектов последующих глав.

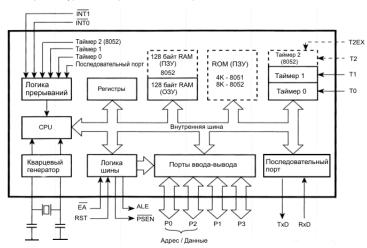

Аппаратная архитектура 8051 представлена на рис. 1.1.

Рис. 1.1. Функциональная схема аппаратной части 8051

В микроконтроллере 8051 все вычисления выполняются в арифметико-логическом устройстве, являющемся частью базового процессорного модуля (CPU). Обмен данными, находящимися в оперативной памяти микроконтроллера, а также считывание команд выполняется по внутренней шине 8051. По этой шине осуществляется и обмен данными с портами ввода/вывода P1 – P3, с последовательным портом и таймерами. Внутренний контроллер шины формирует необходимые сигналы (EA, ALE, PSEN, RD/WR) для работы с внешней памятью программ и данных, а также сигнал сброса/начальной установки RST.

Микроконтроллеры 8051 рассчитаны на работу с системами реального времени, которые могут генерировать определенные сигналы, требующие немедленной реакции микроконтроллера. Для обработки таких сигналов (или событий) служит аппаратно реализованная логика прерываний, позволяющая обрабатывать сигналы внешних источников, таймеров и последовательного порта.

Скорость выполнения операций в системе на базе 8051 зависит от тактовой частоты, с которой работает кристалл и которая может варьироваться от единиц до нескольких десятков мегагерц. В архитектуру классического микроконтроллера 8051 были внесены некоторые изменения (к двум существующим таймерам добавлен третий, а также расширена внутренняя память), которые привели к созданию устройства 8052, наиболее популярного в настоящее время.

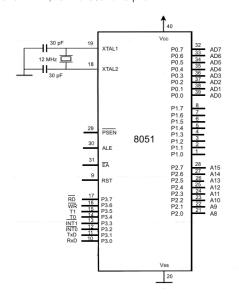

Микроконтроллер 8051 реализован в виде однокристального устройства с внешними выводами, обозначенными, как показано на рис. 1.2.

**Рис. 1.2.** Схема расположения выводов 8051

Входные и выходные сигналы микроконтроллера 8051 имеют следующие назначения:

- XTAL и XTAL2 входы подключения кварцевого резонатора для работы генератора тактовой частоты микроконтроллера;

- PSEN сигнал, используемый при обращении к внешней памяти программ:

- ALE выходной сигнал разрешения фиксации адреса при обращении к внешней памяти программ/данных;

- ЕА сигнал, блокирующий работу с внутренней памятью;

- RST сигнал общего сброса;

- P0 P3 выводы портов ввода/вывода микроконтроллера;

- Vss и Vcc выводы подачи напряжения питания.

Порты PO, P2 и P3 помимо функционирования в режиме ввода/вывода дискретных сигналов могут выполнять, в зависимости от аппаратной конфигурации, и другие функции. Так, через порт PO при обращениях к внешней памяти выставляются младшие 8 бит 16-разрядного адреса, а затем, в фазе записи/чтения данных, через этот порт идет обмен данными. Порт P2 при обращениях к внешней памяти служит источником старших 8 бит 16-разрядного адреса.

Выводы порта РЗ микроконтроллера 8051 имеют следующие альтернативные назначения:

- РЗ.О вход приема данных в последовательный порт;

- РЗ.1 выход передачи данных с последовательного порта;

- РЗ.2 вход внешнего прерывания INTO;

- Р3.3 вход внешнего прерывания INT1;

- РЗ.4 вход управления таймером 0:

- Р3.5 вход управления таймером 1;

- РЗ.6 выход сигнала записи в память;

- Р3.7 выход сигнала чтения из памяти.

Для использования альтернативных функций порта P3 необходимо настроить соответствующим образом программное обеспечение системы 8051.

## 1.1. Структура внутренней памяти 8051

Микроконтроллеры 8051 оперируют двумя типами памяти: памятью программ и памятью данных. Память данных может быть реализована как комбинация размещенного на кристалле (резидентного или on-chip) статического 03У и внешних микросхем памяти. Для простых аппаратно-программных конфигураций с применением 8051 бывает достаточно резидентной памяти самого микроконтроллера.

Программный код размещается в памяти программ, которая физически может быть реализована в виде однократно программируемого устройства (EPROM), перепрограммируемого устройства (EEPROM) или флеш-памяти. Если для записи программ используется EPROM или EEPROM, то программный код обычно располагается во внешнем по отношению к микроконтроллеру устройстве. В подавляющем большинстве современных микроконтроллеров 8051 память программ располагается во флеш-памяти, находящейся, так же как и резидентная память данных, на одном кристалле.

Память программ и память данных физически и логически разделены, имеют различные механизмы адресации, работают под управлением различных сигналов и выполняют разные функции.

Память программ может иметь максимальный объем, равный 64 Кб, что обусловлено использованием 16-разрядной шины адреса. Во многих случаях емкость памяти программ, размещенной на кристалле 8051, ограничена 4, 8 или 16 Кб. В память программ кроме команд могут записываться константы, управляющие слова инициализации, таблицы перекодировки входных и выходных переменных и т.п. Доступ к содержимому памяти программ осуществляется посредством 16-битовой шины адреса. Сам адрес формируется с помощью либо программного счетчика (РС), либо регистра-указателя данных (DPTR). DPTR выполняет функции базового регистра при косвенных переходах по программе или используется в операциях с таблицами.

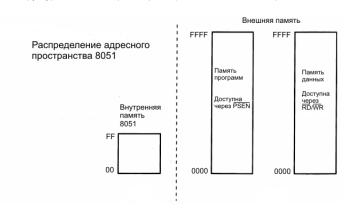

Общая структура памяти микроконтроллера 8051 показана на рис. 1.3.

Рис. 1.3. Общая структура памяти

Рассмотрим более подробно резидентную (on-chip) память микроконтроллера 8051. Резидентная память, изображенная в левой части рис. 1.3, состоит из двух частей: внутреннего 03У размером 128 байт и памяти, выделяемой для регистров специальных функций (Special Function Registers, SFR). Внутреннее 03У имеет структуру, показанную на рис. 1.4.

Распределение внутренней памяти 8051 Адреса битов Адреса битов 3F 3E 3D 3C 3B 3A 39 38 7F с битовой адресацией 26 37 36 35 34 33 32 31 30 2F 2E 2D 2C 2B 2A 29 28 Область памяти Область 24 27 26 25 24 23 22 21 20 23 IF IE ID IC IB IA 19 18 общего назначения 22 17 16 15 14 13 12 11 10 0F 0E 0D 0C 0B 0A 09 08 07 06 05 04 03 02 01 00 30 7F 7E 7D 7C 7B 7A 79 78 2F с битовой Банк 3 2E 77 76 75 74 73 72 71 70 17 6F 6E 6D 6C 6B 6A 69 68 2D Банк 2 2C 67 66 65 64 63 62 61 60 10 адреса 2B 5F 5E 5D 5C 5B 5A 59 58 Банк 1 2A 57 56 55 54 53 52 51 50 08 07 Банк 0 (по умолчанию) Регистры R0 – R7 29 4F 4E 4D 4C 4B 4A 49 48 28 47 46 45 44 43 42 41 40 **Рис. 1.4.**Внутреннее ОЗУ

Для доступа к данным, размещенным во внутреннем 03У, используется однобайтовый адрес. Архитектура внутренней памяти данных 8051 позволяет обращаться к отдельным битам данных в специально выделенной области внутреннего 03У, начиная с адреса 0х20 и заканчивая 0х2F (см. рис. 1.4). Таким образом, в указанном диапазоне адресов можно обращаться к 128-битовым переменным с помощью команд битовых операций SETB и CLR. Битовые переменные нумеруются, начиная с 0х0 и заканчивая 0х7F. Это не означает, что нельзя обращаться к этим ячейкам памяти, как к байтам при обычных операциях с памятью.

Например, для установки бит 0 и 1 в области памяти начиная с 0x20, можно выполнить команды

| SETB | 00h |  |  |

|------|-----|--|--|

| SETB | 01h |  |  |

#### или команду

```

ORL 20h, 0x3

```

Во втором случае обращение выполняется к байту по адресу 0x20, а установка соответствующих битов выполняется операцией «логическое ИЛИ».

Во внутреннем ОЗУ микроконтроллера 8051 выделены 4 банка регистров общего назначения. При включении микроконтроллера банком по умолчанию становится банк 0 (см. рис. 1.4). При этом регистру R0 соответствует адрес 0х00, регистру R1 – адрес 0х01, наконец, регистру R7 при использовании банка 0 соответствует адрес 0х07. Если банком по умолчанию становится, например, банк 1, то регистру R0 будет соответствовать адрес 0х08, регистру R1 – адрес 0х09 и регистру R7 – адрес 0х0F.

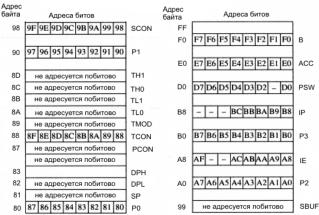

К адресному пространству внутреннего ОЗУ начиная с адреса 0x80 примыкают и адреса регистров специальных функций (рис. 1.5).

Регистры специальных функций (Special Function Registers, SFR) предназначены для управления ходом вычислительных операций, а также отвечают за инициализацию, настройку и управление портами ввода/вывода, таймерами, последовательным портом. Кроме того, регистры специальных функций содержат информацию о приоритетах прерываний, а также биты

управления разрешением прерываний. Регистры специальных функций с указанием их назначения перечислены в табл. 1.1.

Рис. 1.5. Регистры специальных функций

Таблица 1.1.

Назначение регистров специальных функций

| Обозначение | Описание                              | Адрес |

|-------------|---------------------------------------|-------|

| А           | Аккумулятор                           | 0E0H  |

| В           | Регистр-расширитель аккумулятора      | 0F0H  |

| PSW         | Слово состояния программы             | 0D0H  |

| SP          | Регистр-указатель стека               | 81H   |

| DPTR        | Регистр-указатель данных (DPH)        | 83H   |

| DPTK        | (DPL)                                 | 82H   |

| P0          | Порт О                                | 80H   |

| P1          | Порт 1                                | 90H   |

| P2          | Порт 2                                | OAOH  |

| P3          | Порт 3                                | 0B0H  |

| IP          | Регистр приоритетов прерываний        | 0B8H  |

| ΙΕ          | Регистр маски прерываний              | 0A8H  |

| TMOD        | Регистр режима таймера/счетчика       | 89H   |

| TCON        | Регистр управления/статуса таймера    | 88H   |

| TH0         | Таймер 0 (старший байт)               | 8CH   |

| TLO         | Таймер 0 (младший байт)               | 8AH   |

| TH1         | Таймер 1 (старший байт)               | 8DH   |

| TL1         | Таймер 1 (младший байт)               | 8BH   |

| SCON        | Регистр управления приемопередатчиком | 98H   |

| SBUF        | Буфер приемопередатчика               | 99H   |

| PCON        | Регистр управления мощностью          | 87H   |

Некоторые регистры специальных функций допускают побитовую адресацию. При этом обращение к отдельным битам такого регистра возможно как с помощью обычных функций для работы с байтами, так и с помощью команд побитовых операций. Например, для запуска таймера 0 можно выполнить команду ассемблера

ORL TCON, #10h

или одну из команд установки бита TCON.4 (TRO):

| SETB | TCON.4 |

|------|--------|

| SETB | TR0    |

Рассмотрим смысл некоторых регистров специальных функций и начнем с аккумулятора и регистра слова состояния (регистра флагов).

Аккумулятор (A) является источником операнда и фиксирует результат при выполнении арифметических, логических операций и ряда операций передачи данных. Кроме того, некоторые операции можно выполнить только с использованием аккумулятора: например, операции сдвигов, проверку на нуль, формирование флага паритета и т.п.

В распоряжении программиста имеются 8 регистров общего назначения R0-R7 одного из четырех банков. При выполнении многих команд в арифметико-логическом устройстве микроконтроллера формируется ряд признаков операции (флагов), которые фиксируются в регистре PSW. Перечень флагов PSW, их символические имена и условия формирования приведены в табл. 1.2.

Обозначение Бит Описание Флаг переноса. Устанавливается и сбрасывается аппаратно C PSW.7 или программно при выполнении арифметических и логических операций Флаг вспомогательного переноса. Устанавливается и сбра-AC PSW.6 сывается только аппаратно при выполнении команд сложения и вычитания и сигнализирует о переносе или займе в бите 3 Флаг О. Может быть установлен, сброшен или проверен PSW.5 F0 программой как флаг, специфицируемый пользователем RS1 PSW.4 Выбор банка регистров. Устанавливается и сбрасывается программно для выбора рабочего банка регистров (табл. 1.3) RS<sub>0</sub> PSW.3 Флаг переполнения. Устанавливается и сбрасывается Ô٧ PSW 2 аппаратно при выполнении арифметических операций PSW.1 Не используется Флаг четности. Устанавливается и сбрасывается аппаратно Ρ PSW.0 в каждом цикле и фиксирует нечетное/четное число единичных битов в аккумуляторе, т.е. выполняет контроль по четности

Установки битов RS0 – RS1 при выборе банка регистров показаны в табл. 1.3.

| RS1 | RS0 | Банк | Границы адресов |

|-----|-----|------|-----------------|

| 0   | 0   | 0    | 00h-07h         |

| 0   | 1   | 1    | 08h-0Fh         |

| 1   | 0   | 2    | 10h-17h         |

| 1   | 1   | 3    | 18h-1Fh         |

Среди регистров специального назначения есть регистры, выполняющие функции адресации данных, находящихся в памяти. К ним относятся 8-разрядный указатель стека (SP) и регистр-указатель DPTR.

Таблица 1.2.

Регистр слова состояния микроконтроллера

Указатель стека может адресовать любую область внутренней памяти данных микроконтроллера, при этом содержимое этого регистра инкрементируется перед выполнением команд PUSH и CALL и декрементируется после выполнения команд POP и RET. В процессе инициализации микроконтроллера после сигнала RST в указатель стека автоматически загружается код 0x07. Это значит, что если программа не переопределяет содержимое указателя стека, то первый элемент данных в стеке будет располагаться в ячейке памяти 0x08.

Нужно отметить одну важную особенность: при загрузке данных в стек адрес растет вверх, поэтому если в программе используются банки 1, 2 или 3, то указатель стека следует проинициализировать адресом из неиспользуемой области памяти, например 0х30, чтобы не перезаписать содержимое регистров одного из банков.

Двухбайтный регистр-указатель данных DPTR обычно используется для фиксации 16-разрядного адреса в операциях с обращением к внешней памяти. При работе с DPTR допускается использование старшего и младшего байтов регистра (DPH и DPL соответственно).

### 1.2. Подключение внешней памяти программ и данных

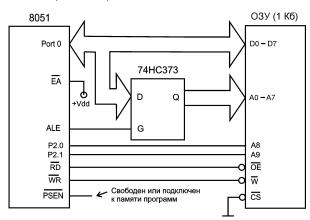

Внешняя память данных может быть подключена к микроконтроллеру приблизительно по такой схеме, какая изображена на рис. 1.6.

Рис. 1.6. Подключение внешней памяти данных

Здесь показан интерфейс микроконтроллера 8051 с внешним модулем 03У емкостью 1 Кб. Адресация памяти по этой схеме реализована следующим образом:

- 1. Младшие 8 бит адреса выводятся стандартным образом через порт P0 и запоминаются в регистре-защелке 74HC373 по спаду сигнала ALE.

- 2. На шину адреса подаются старшие биты адреса, из которых используются разряды A8 и A9, устанавливаемые на выводах P2.0 и P2.1 и предназначенные (вместе с установленными в регистре 74HC373 линиями A0 A7) для выбора адреса в пределах 1 Кб.

- 3. По низкому уровню одного из сигналов RD (чтение) или WR (запись) осуществляется требуемая операция, при этом байт данных считывается/записывается через порт PO.

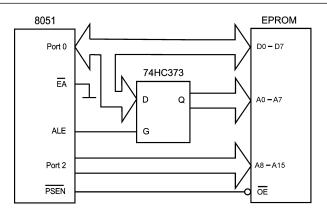

Память программ, так же как и память данных, может быть расширена до 64 Кб путем подключения внешних микросхем. Стандартная схема подключения внешней памяти программ осуществляется по схеме, показанной на рис. 1.7.

Рис. 1.7.

Подключение внешней памяти программ

Так же как и при обращении к памяти данных, младшая часть адреса памяти формируется портом P0 и запоминается в регистре-защелке по спаду ALE, а старший байт адреса выводится через порт P2. Считывание команды выполняется при подаче низкого уровня на линию PSEN. Поскольку вывод EA подключен к общему проводу, то внутренняя память программ отключается и микроконтроллер при включении начинает выполнение программы с адреса 0х0000 внешней памяти.

## 1.3. Система команд микроконтроллера семейства 8051

Микроконтроллеры семейства 8051 являются микропроцессорными устройствами с архитектурой CISC со стандартным набором команд, характерных для данной архитектуры. Система команд 8051-совместимых устройств включает 111 основных команд размером от одного до трех байт, но большая часть этих команд – одно- или двухбайтовая. Почти все команды выполняются за один или два машинных цикла, что по времени приблизительно равно 1-2 мкс при тактовой частоте 12 МГц, за исключением команд умножения и деления, которые требуют для выполнения четыре машинных цикла.

Команды микроконтроллеров 8051 используют прямую, непосредственную, косвенную и неявную адресацию данных. При этом в качестве операндов команд могут выступать отдельные биты, четырехбитовые комбинации (тетрады), байты и слова из двух байт.

В набор команд семейства 8051 входит ряд команд, обеспечивающих выполнение специфичных функций управления, например, манипуляции с отдельными битами. Особенностью системы команд 8051 является возможность адресации отдельных бит в памяти данных, а также отдельных бит регистров специальных функций.

По выполняемым функциям команды микроконтроллера 8051 можно разделить на несколько групп:

- пересылки данных;

- арифметических операций;

- логических операций:

- операций над битами;

- передачи управления.

Рассмотрим эти группы команд более подробно, но перед этим условимся при описании мнемоники команд использовать следующие обозначения:

- - Rn (n = 0...7) регистр общего назначения в выбранном банке регистров;

- @Ri (i = 0, 1) регистр общего назначения в выбранном банке регистров, используемый для формирования косвенного адреса;

- addr адрес байта;

- src адрес байта-источника;

- dst адрес байта-приемника;

- addr11 11-разрядный абсолютный адрес перехода;

- addr16 16-разрядный абсолютный адрес перехода;

- label относительный адрес перехода;

- #direct8 непосредственный операнд размером 1 байт;

- #direct16 непосредственный операнд размером 2 байта;

- bit адрес прямо адресуемого бита;

- ~bit инверсия прямо адресуемого бита;

- A регистр-аккумулятор;

- PC регистр-счетчик команд;

- DPTR 16-разрядный регистр-указатель данных;

- () содержимое ячейки памяти или регистра.

Команды пересылки данных микроконтроллера 8051 включают 28 команд, краткое описание которых приведено в табл. 1.4.

#### Таблица 1.4. Команды пересылки данных

| Мнемоника           | Описание                                                    |  |

|---------------------|-------------------------------------------------------------|--|

| MOV A, Rn           | (A) ← (Rn)                                                  |  |

| MOV A, addr         | $(A) \leftarrow (addr)$                                     |  |

| MOV A, @Ri          | (A) ← ((Ri))                                                |  |

| MOV A, #direct8     | (A) ← #direct8                                              |  |

| MOV Rn, A           | (Rn) ← (A)                                                  |  |

| MOV Rn, addr        | $(Rn) \leftarrow (addr)$                                    |  |

| MOV Rn, #direct8    | (Rn) ← #direct8                                             |  |

| MOV add, A          | $(addr) \leftarrow (A)$                                     |  |

| MOV add, Rn         | $(addr) \leftarrow (Rn)$                                    |  |

| MOV dst, src        | (dst) ← (src)                                               |  |

| MOV addr, @Ri       | $(addr) \leftarrow ((Ri))$                                  |  |

| MOV addr, #direct8  | (addr) ← #direct8                                           |  |

| MOV @Ri, A          | $((Ri)) \leftarrow (A)$                                     |  |

| MOV @Ri, addr       | $((Ri)) \leftarrow (addr)$                                  |  |

| MOV @Ri, #direct8   | ((Ri)) ← #direct8                                           |  |

| MOV DPTR, #direct16 | (DPTR) ← #direct16                                          |  |

| MOVC A, @A+DPTR     | $(A) \longleftarrow ((A) + (DPTR))$                         |  |

| MOVC A, @A+PC       | $(PC) \longleftarrow (PC+1), (A) \longleftarrow ((A)+(PC))$ |  |

| MOVX A, @Ri         | $(A) \leftarrow ((Ri))$                                     |  |

| MOVX A, @DPTR       | $(A) \leftarrow ((DPTR))$                                   |  |

#### СИСТЕМА КОМАНД МИКРОКОНТРОЛЛЕРА СЕМЕЙСТВА 8051

| Мнемоника     | Описание                                             |

|---------------|------------------------------------------------------|

| MOVX @Ri, A   | $((Ri)) \leftarrow (A)$                              |

| MOVX @DPTR, A | $((DPTR)) \leftarrow (A)$                            |

| PUSH addr     | $(SP) \leftarrow (SP) + 1, ((SP)) \leftarrow (addr)$ |

| POP addr      | $(addr) \leftarrow ((SP)), (SP) \leftarrow (SP) - 1$ |

| XCH A, Rn     | $(A) \longleftrightarrow (Rn)$                       |

| XCH A, addr   | $(A) \longleftrightarrow (addr)$                     |

| XCH A, @Ri    | (A) ↔ ((@Ri))                                        |

| XCHD A, @Ri   | (A0 − 3) ↔ ((@Ri0 − 3))                              |

| MOV A, Rn     | (A) ← (Rn)                                           |

Таблица 1.4. Команды пересылки данных (окончание)

Команда MOV выполняет пересылку данных из второго операнда в первый. Эта команда не работает с данными, находящимися во внешней памяти данных или в памяти программ. Для работы с данными, находящимися во внешней памяти данных, предназначены команды MOVX, а для работы с константами, записанными в память программ, – команда MOVC. Первая из них обеспечивает чтение/запись байтов из внешней памяти данных, вторая – чтение байтов из памяти программ.

Команды XCH выполняют обмен байтами между аккумулятором и ячейкой памяти, а команда XCHD выполняет обмен данными между младшими тетрадами (биты 0-3).

Команды PUSH и POP предназначены для записи данных в стек и их чтения из стека соответственно. При этом размер стека ограничен лишь размером памяти данных, расположенной на кристалле. В процессе инициализации микроконтроллера после сигнала сброса или при включении питающего напряжения в указатель стека SP заносится код 07H. Таким образом, первый элемент стека будет располагаться в ячейке памяти с адресом 08H.

В группе команд пересылок микроконтроллера нет команд для работы с регистрами специальных функций (таймерами, портами ввода/вывода и т.д.). Доступ к таким регистрам осуществляется по их прямому адресу или с использованием их мнемоники, записанной в специальном файле (для программ на ассемблере, например, таким файлом может быть 8051.MCU).

Следует отметить, что регистр-аккумулятор имеет два различных имени в зависимости от способа адресации (A – при неявной адресации, например MOV A, RO; ACC – при использовании прямого адреса).

В группу команд арифметических операций 8051 входят 24 команды, выполняющие операции по обработке целочисленных данных, включая команды умножения и деления. Перечень команд этой группы приведен в табл. 1.5.

| Мнемоника       | Описание                                |

|-----------------|-----------------------------------------|

| ADD A, Rn       | $(A) \leftarrow (A) + (Rn)$             |

| ADD A, addr     | $(A) \leftarrow (A) + (addr)$           |

| ADD A, @Ri      | $(A) \longleftarrow (A) + ((Ri))$       |

| ADD A, #direct8 | (A) ← (A) + #direct8                    |

| ADDC A, Rn      | $(A) \longleftarrow (A) + (Rn) + (C)$   |

| ADDC A, addr    | $(A) \leftarrow (A) + (addr) + (C)$     |

| ADDC A, @Ri     | $(A) \longleftarrow (A) + ((Ri)) + (C)$ |

Таблица 1.5. Команды арифметических операций

Таблица 1.5. Команды арифметических операций (окончание)

| Мнемоника        | Описание                                      |

|------------------|-----------------------------------------------|

| ADDC A, #direct8 | (A) ← (A) + #direct8 + (C)                    |

| DAA              | Десятичная коррекция аккумулятора             |

| SUBB A, Rn       | $(A) \longleftarrow (A) - (Rn) - (C)$         |

| SUBB A, addr     | $(A) \leftarrow (A) - (ad) - (C)$             |

| SUBB A, @Ri      | $(A) \longleftarrow (A) - ((Ri)) - (C)$       |

| SUBB A, #direct8 | (A) ← (A) − #direct8 − (C)                    |

| INC A            | $(A) \leftarrow (A) + 1INC Rn(Rn) < (Rn) + 1$ |

| INC Rn           | (Rn) ← (Rn) + 1                               |

| INC addr         | (addr) ← (addr) + 1                           |

| INC @Ri          | ((Ri)) ← ((Ri)) + 1                           |

| INC DPTR         | $(DPTR) \leftarrow (DPTR) + 1$                |

| DEC A            | (A) ← (A) − 1                                 |

| DEC Rn           | (Rn) ← (Rn) − 1                               |

| DEC addr         | (addr) ← (addr) - 1                           |

| DEC @Ri          | ((Ri)) ← ((Ri)) − 1                           |

| MUL AB           | $(B)(A) \longleftarrow (A) \times (B)$        |

Результат выполнения команд ADD, ADDC, SUBB, MUL и DIV влияет на флаги слова состояния (PSW) следующим образом:

- флаг переноса С устанавливается при переносе из разряда D7 в том случае, если результат операции не помещается в восемь разрядов; флаг дополнительного переноса АС устанавливается при переносе из разряда D3 в командах сложения и вычитания и служит для реализации десятичной арифметики. Этот признак используется командой DAA;

- флаг OV устанавливается при переносе из разряда D6 в случае, если результат операции не помещается в семь разрядов и восьмой не может быть интерпретирован как знаковый. Этот признак служит для организации обработки чисел со знаком;

- флаг четности Р устанавливается и сбрасывается аппаратно. Если число единичных битов в аккумуляторе нечетно, то P = 1, в противном случае P = 0.

Следующая группа команд, которую мы рассмотрим, – это команды логических операций. Группа содержит 25 команд (табл. 1.6).

Таблица 1.6. Команды логических операций

|       | r pyrma ddaphan 20 Nomana (1809) |                                    |  |

|-------|----------------------------------|------------------------------------|--|

| :     | Мнемоника                        | Описание                           |  |

|       | ANL A, Rn                        | (A) ← (A) & (Rn)                   |  |

|       | ANL A, addr                      | (A) ← (A) & (addr)                 |  |

|       | ANL A, @Ri                       | (A) ← (A) & ((Ri))                 |  |

|       | ANL A, #direct8                  | (A) ← (A) & (#direct8)             |  |

|       | ANL addr, A                      | $(addr) \leftarrow (addr) \& (A)$  |  |

|       | ANL addr, #direct8               | (addr) ← (addr) & (#direct8)       |  |

|       | ORL A, Rn                        | $(A) \longleftarrow (A) \mid (Rn)$ |  |

| N. N. | ORL A, addr                      | $(A) \leftarrow (A) \mid (addr)$   |  |

#### СИСТЕМА КОМАНД МИКРОКОНТРОЛЛЕРА СЕМЕЙСТВА 8051

| Мнемоника          | Описание                          |

|--------------------|-----------------------------------|

| ORL A, @Ri         | $(A) \leftarrow (A) \mid (Ri)$    |

| ORL A, #direct8    | (A) ← (A)   (#direct8)            |

| ORL addr, A        | (addr) ← (addr) I (A)             |

| ORL addr, #direct8 | (addr) ← (addr) I (#direct8)      |

| XRL A, Rn          | (A) ← (A) ^ (Rn)                  |

| XRL A, addr        | $(A) \leftarrow (A) \land (addr)$ |

| XRL A, @Ri         | $(A) \leftarrow (A) \land ((Ri))$ |

| XRL A, #direct8    | (A) ← (A) ^ (#direct8)            |

| XRL addr, A        | (addr) ← (addr) ^ (A)             |

| XRL addr, #direct8 | (addr) ← (addr) ^ (#direct8)      |

| CLR A              | (A) ← 0                           |

| CPL A              | (A) ← ~(A)                        |

| SWAP A             | (A0-3) - (A4-7)                   |

| RL A               | Циклический сдвиг влево           |

| RLC A              | Сдвиг влево через перенос         |

| RR A               | Циклический сдвиг вправо          |

| RRC A              | Сдвиг вправо через перенос        |

Таблица 1.6 Команды логических операций (окончание)

Команды логических операций манипулируют байтами и позволяют выполнить следующие операции:

- логическое И (&);

- логическое ИЛИ (1);

- исключающее ИЛИ (^);

- инверсию (~);

- очистку байта;

- обычные и циклические сдвиги.

Команды операций над битами микроконтроллера 8051 включают 12 команд, позволяющих выполнять операции над отдельными битами: сброс, установку, инверсию, а также «логическое И» (&) и «логическое ИЛИ» (I). В качестве операндов могут выступать 128 бит из внутренней памяти данных микроконтроллера, а также регистры специальных функций, допускающие адресацию отдельных битов. Перечень команд и их мнемоника показаны в табл. 1.7.

| Мнемоника  | Описание                      |  |

|------------|-------------------------------|--|

| CLR C      | (C) ← 0                       |  |

| CLR bit    | (bit) ← 0                     |  |

| SETB C     | (C) ← 1                       |  |

| SETB bit   | (bit) ← 1                     |  |

| CPL C      | (C) ← ~(C)                    |  |

| CPL bit    | (bit) ← ~ (bit)               |  |

| ANL C, bit | $(C) \leftarrow (C) \& (bit)$ |  |

Таблица 1.7. Команды битовых операций

Таблица 1.7.

Команды битовых операций (окончание)

| Мнемоника  | Описание                        |

|------------|---------------------------------|

| ORL C, bit | $(C) \leftarrow (C) \mid (bit)$ |

| MOV C, bit | $(C) \leftarrow (bit)$          |

| MOV bit, C | (bit) ← (C)                     |

Последняя группа команд, которую мы рассмотрим, – это группа команд передачи управления микроконтроллера. В группе представлены команды безусловного и условного переходов, команды вызова подпрограмм и команды возврата из подпрограмм. Мнемоника команд и их описание представлены в табл. 1.8.

Таблица 1.8. Команды передачи управления

| Мнемоника                 | Описание                                                                    |

|---------------------------|-----------------------------------------------------------------------------|

| LJMP addr16               | Длинный безусловный переход по всем адресам памяти                          |

| AJMP addr11               | Безусловный переход в пределах страницы 2 Кб                                |

| SJMP label                | Безусловный переход на метку label в пределах страниць 256 байт             |

| JMP @A+DPTR               | Безусловный переход по косвенному адресу                                    |

| JZ label                  | Переход на метку label, если нуль                                           |

| JNZ label                 | Переход на метку label, если не нуль                                        |

| JC label                  | Переход на метку label, если бит переноса установлен                        |

| JNC label                 | Переход на метку label, если бит переноса не установлен                     |

| JB bit, label             | Переход на метку label, если бит установлен                                 |

| JNB bit, label            | Переход на метку label, если бит не установлен                              |

| JBC bit, label            | Переход на метку label, если бит установлен с очисткой бита                 |

| DJNZ Rn, label            | Переход на метку label, если содержимое Rn не равно                         |

| ODJNZ addr, label         | Переход на метку label, если содержимое addr не равно                       |

| OCJNE A, addr, label      | Сравнение аккумулятора с байтом и переход на метку label, если не равно     |

| CJME A, #direct8, label   | Сравнение аккумулятора с константой и переход на метку label, если не равно |

| CJNE Rn, #direct8, label  | Сравнение регистра с константой и переход на метку label, если не равно     |

| CJNE @Ri, #direct8, label | Сравнение байта памяти с константой и переход на метку label, если не равно |

| LCALL addr16              | Длинный вызов подпрограммы по всем адресам памяти                           |

| ACALL addr11              | Вызов подпрограммы в пределах страницы 2 Кб                                 |

| RET                       | Возврат подпрограммы                                                        |

| RETI                      | Возврат подпрограммы обработки прерывания                                   |

| NOP                       | Пустая операция                                                             |

Рассмотрим, как работают команды передачи управления. Команда безусловного перехода LJMP осуществляет переход по абсолютному 16-битному адресу в пределах сегмента программ.

Действие команды АЈМР аналогично команде LJMP, однако операндом являются лишь 11 младших разрядов адреса, что позволяет выполнить переход в пределах страницы размером 2 Кб. При этом содержимое счетчика команд вначале увеличивается на 2, затем заменяются 11 разрядов адреса.

В команде SJMP указан не абсолютный, а относительный адрес перехода. Величина смещения label рассматривается как число со знаком, поэтому переход возможен в пределах от -128 до +127 байт относительно адреса команды, следующей за командой SJMP.

Команда косвенного перехода JMP @A+DPTR позволяет вычислять адрес перехода в процессе выполнения самой программы. С помощью команд условного перехода можно проверять следующие условия:

- аккумулятор содержит нулевое значение (JZ);

- аккумулятор содержит ненулевое значение (JNZ);

- бит переноса С установлен (JC);

- бит переноса С не установлен (JNC);

- прямо адресуемый бит равен 1 (JB);

- прямо адресуемый бит равен 0 (JNB);

- прямо адресуемый бит равен 1 и очищается при выполнении команды (JBC).

Все команды условного перехода микроконтроллера 8051 оперируют с коротким относительным адресом из диапазона –128 – +127 относительно следующей команды.

Команда DJNZ предназначена для организации программных циклов. Указанные в команде регистр Rn или байт по адресу addr содержат счетчик повторений цикла, а смещение label – относительный адрес перехода к началу цикла. При выполнении команды содержимое счетчика уменьшается на 1 и проверяется на 0. Если значение содержимого счетчика не равно 0, то осуществляется переход на начало цикла, в противном случае выполняется следующая команда.

Команда СЈNЕ удобна для реализации процедур ожидания событий. Операнды команды сравниваются между собой, после чего, в зависимости от результата сравнения, выполняется либо переход на метку label, либо выполняется следующая команда.

Действие команд вызова процедур полностью аналогично действию команд безусловного перехода — за исключением того, что они сохраняют в стеке адрес возврата.

Команда возврата из подпрограммы RET восстанавливает из стека значение содержимого счетчика команд, а команда возврата из процедуры обработки прерывания RETI, кроме того, разрешает прерывания. Следует отметить, что ассемблер 8051 допускает обобщенную мнемонику для команд безусловного перехода JMP и вызова подпрограмм CALL.

## 1.4. Система прерываний

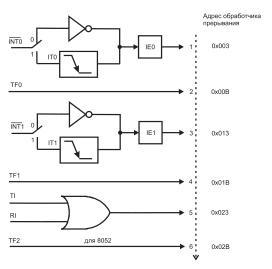

Работа микроконтроллера 8051 в системах реального времени была бы невозможна без обработки событий, генерируемых внешними устройствами, и установки временных зависимостей между событиями в системе. Именно этим целям и служит логика обработки прерываний 8051, функциональная схема которой показана на рис. 1.8.

Классический микроконтроллер 8051 имеет 5 источников прерываний: два внешних прерывания, инициированных сигналами на входах, – INTO (вывод P3.2) и INT1 (вывод P3.3); два прерывания таймеров – 0 и 1; прерывание последовательного порта (см. рис. 1.8). Очередность выполнения двух и более одновременно поступивших прерываний определяется их приоритетами.

**Рис. 1.8.** Структура прерываний 8051

Если предположить, что все прерывания имеют одинаковые установки приоритета, то при одновременном возникновении нескольких прерываний они обрабатываются так, как показано на рис. 1.8. Например, прерывание INTO имеет наивысший приоритет (ему соответствует условное обозначение 1 на рис. 1.8), прерывание таймера 0 имеет более низкий приоритет по сравнению с INTO (обозначено цифрой 2) и т.д. Самый низкий приоритет в устройстве 8051 имеет прерывание последовательного порта (обозначено цифрой 5 на рисунке). Для микроконтроллера 8052 самым низким приоритетом обладает прерывание таймера 2 (обозначено цифрой 6). Для изменения приоритетов выполнения прерываний следует устанавливать специальные флаги в регистре приоритетов IP (табл. 1.9).

Таблица 1.9. Регистр приоритетов

| Обозначение | Бит регистра IP | Описание                                                                                                                                        |

|-------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| PX0         | IP.0            | Бит приоритета внешнего прерывания 0.<br>Установка/сброс программой для назначения<br>прерыванию INTO высшего/низшего приоритета                |

| PTO         | IP.1            | Бит приоритета таймера О. Установка/сброс программой для назначения прерыванию от таймера О высшего/низшего приоритета                          |

| PX1         | IP.2            | Бит приоритета внешнего прерывания 1.<br>Установка/сброс программой для назначения<br>прерыванию INT1 высшего/низшего приоритета                |

| PT1         | IP.3            | Бит приоритета таймера 1. Установка/сброс программой для назначения прерыванию от таймера 1 высшего/низшего приоритета                          |

| PS          | IP.4            | Бит приоритета последовательного порта. Установка/сброс программой для назначения прерыванию последовательного порта высшего/низшего приоритета |

Посмотрим, как вызываются и обрабатываются прерывания. Микроконтроллер реагирует на прерывания, только если будет установлен флаг соответствующего прерывания в регистре TCON (табл. 1.10).

Любое из прерываний будет вызвано только в том случае, если его вызов разрешен путем установки соответствующих битов в регистре IE (табл. 1.11).